作者:lightfall

仅仅是大数据或内存敏感型应用,对CXL的需求还没那么迫切,一次性传输数据的规模与延迟需求呈反比。但是在AI时代,海量数据、低延迟与高带宽的需求同时到来,这才有了靠近CPU或GPU等计算单元的HBM的大行其道。

人工智能(AI)和高性能计算(HPC)应用的GPU,通常内置有限的高带宽内存(HBM),这限制了它们在AI和其他工作负载中的表现。最近,由韩国高等科学技术院(KAIST)支持的Panmnesia公司开发了一种低延迟的CXL(Compute Express Link)IP,实现了两位数纳秒级别的延迟,通过连接到PCIe总线的设备来扩展GPU的内存容量,而不仅仅局限于GPU内置的内存,甚至允许使用固态硬盘(SSDs)来扩展内存容量。

GPU常常需要依赖主机的内存和存储,这就需要在CPU和GPU之间频繁地传输数据,这不但带来大量性能消耗,还极大地阻碍了GPU的普及。这种复杂性来自于用户需要明确管理数据结构、监督分块数据的传输以及协调数据迁移,这些过程可能既繁琐又效率低下。

NVIDIA和AMD通过开发一些工具包等软件支持GPU架构,实现了统一虚拟内存(UVM)。UVM允许CPU和GPU通过统一虚拟地址空间内的共享指针来访问数据,本质上,虚拟空间中的内存是按需分配的。UVM已在各种框架中得到广泛应用,包括TensorFlow2、DGL3和OneAPI4。尽管UVM在提高GPU的易用性方面有其优势,但它可能会引起性能瓶颈。

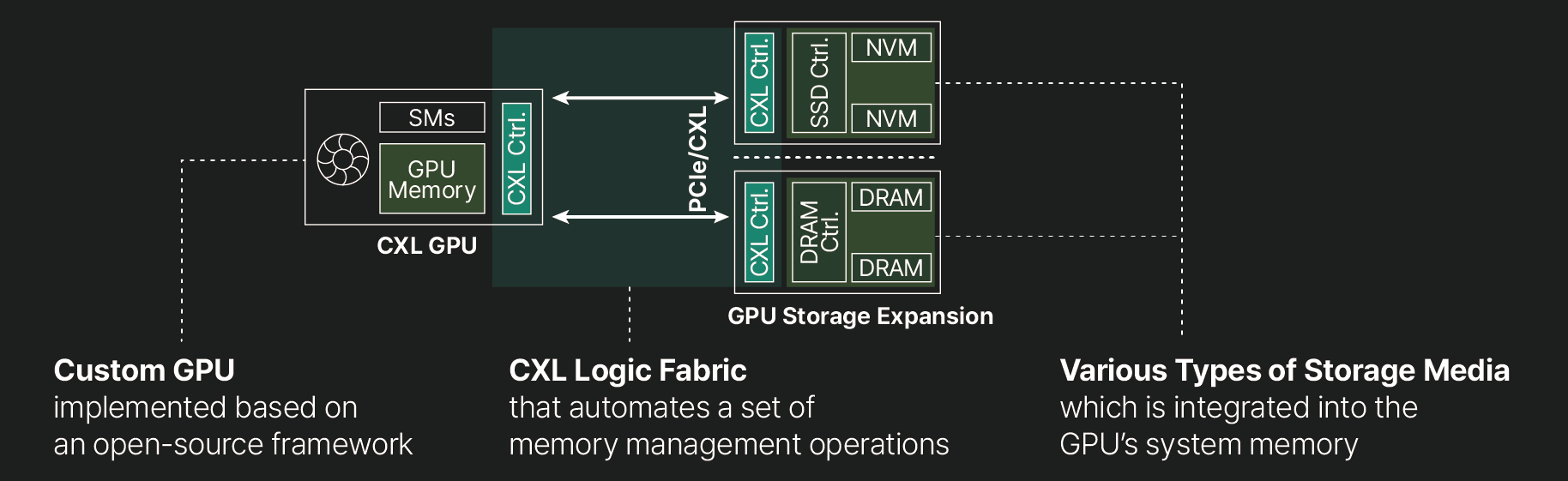

为了解决GPU内存容量的限制并尽量减少性能损失,Panmnesia公司推出了CXL(Compute Express Link)GPU存储扩展技术(见上图)。CXL使用PCIe物理数据链路将称为端点(EPs)的设备映射到主机可以访问的可缓存内存空间。这种配置允许计算单元通过标准内存请求直接访问这些端点。与JEDEC DDR标准定义的DRAM接口的同步通信不同,CXL支持与计算单元的异步通信,类似于块存储设备。这种灵活性使得可以使用包括基于非易失性存储器(NVM)的固态硬盘(SSDs)和动态随机存取存储器(DRAMs)在内的各种存储介质来实现端点。

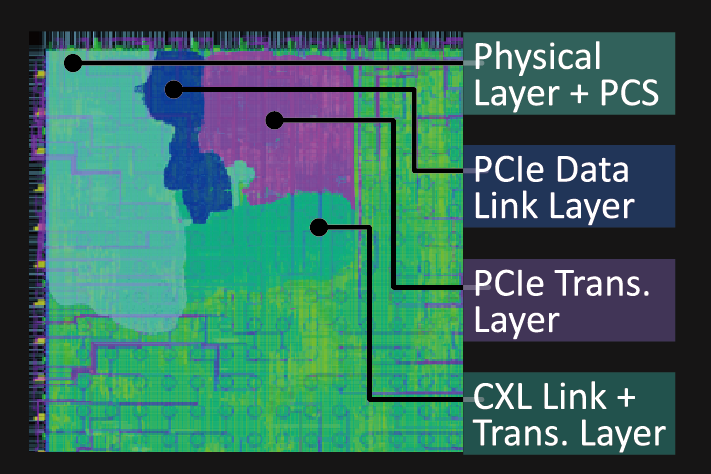

CXL控制器布局(来源:Panmnesia)

集成CXL以扩展GPU存储并不容易,因为GPU中缺少支持DRAM和/或SSD端点的CXL逻辑布线和子系统。此外,GPU的缓存和内存子系统除了统一虚拟内存(UVM)之外,不识别任何扩展,而UVM通常速度较慢。为了解决这个问题,Panmnesia开发了一系列关键硬件层,这些层支持所有主要的CXL子协议,并将它们整合到一个统一的控制器中(见上图)。这个控制器与CXL 3.1兼容,同时提供对早期CXL版本(2.0/1.1)的向后兼容性。Panmnesia表示经过严格的测试,控制器展示了两位数纳秒的往返延迟,包括标准内存操作和CXL flit传输之间的协议转换时间。它已成功集成到硬件RTL级别的内存扩展器和GPU/CPU原型中,证明了其在各种计算硬件中的有效性和兼容性。

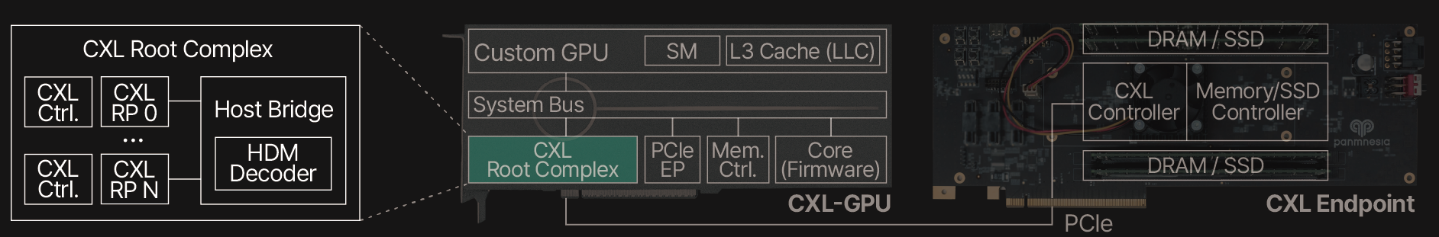

Panmnesia的技术核心是开发了一个符合CXL 3.1标准的根复合体(RC),配备了多个支持通过PCIe连接外部内存的根端口(RPs),以及一个带有主机管理的设备内存(HDM)解码器的主机桥,该解码器连接到GPU的系统总线,如上图所示。HDM解码器负责管理系统内存的地址范围,实际上让GPU的内存子系统“认为”它正在处理系统内存,但实际上,子系统使用的是PCIe连接的DRAM或NAND。这意味着DDR5或SSDs都可以用来扩展GPU的内存池。

使用PCIe连接内存扩展GPU存储的方法是否会大行其道还是未知数,总的来说,CXL支持对AI/HPC GPU有很大帮助,但性能是一个大问题。

无论是英特尔的CPU Max/GPU Max解决方案,还是AMD的显卡集成SSD,还是NV主推的HBM,都缺乏通用性和异构扩展能力。CXL的出现,很好的解决了PCIe框架下的数据传输机制,降低了不参与计算的单元对其他单元数据传输的控制与干扰。在AI大潮中,CXL也得到了飞速发展,进而又促进AI负载在异构架构系统上效率与性能的提升。

奇谱科技

奇谱科技