作者:原创

近日,JEDEC固态技术协会宣布其下一代高带宽内存(HBM)DRAM标准HBM4的最终化工作接近完成。

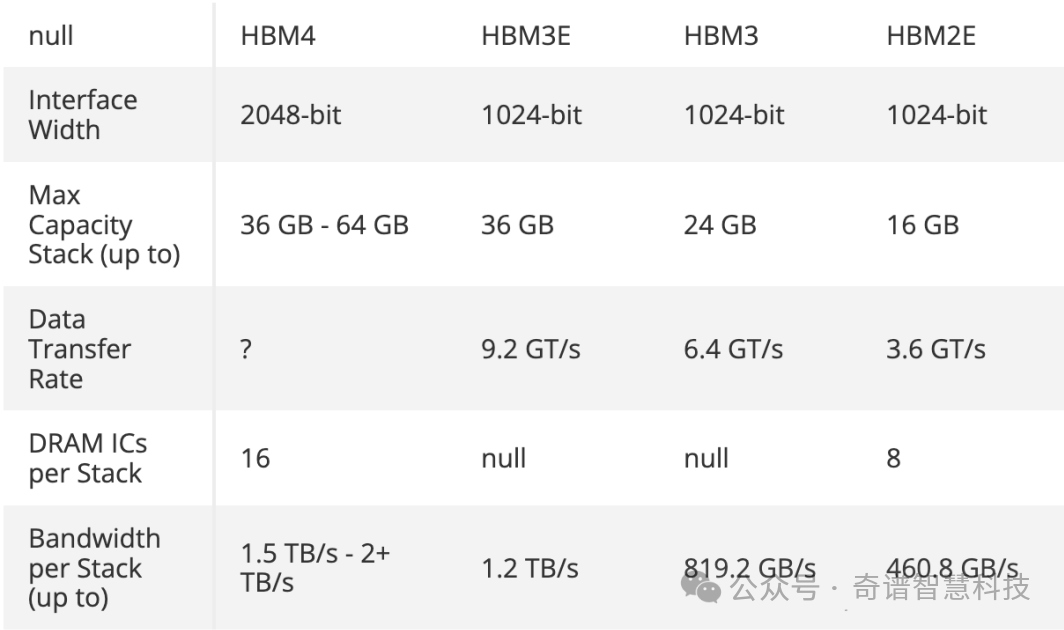

HBM4比上代HBM3标准每个堆栈通道数增加了一倍,物理尺寸更大,能够提供更高的数据传输带宽和更好的并行处理能力。同时,JEDEC为了支持设备兼容性,单个控制器可以同时操作HBM3和HBM4。

HBM4将指定24Gb和32Gb层,并提供4-high、8-high、12-high和16-highTSV堆栈,HBM4通过3D堆叠技术,能够显著提升内存的性能和容量。JEDEC表示,在生成式人工智能(AI)、高性能计算、高端显卡和服务器等领域,这些改进对于需要高效处理大型数据集和复杂计算的应用至关重要。

HBM4将把内存堆栈接口从1024位扩展至2048位,这将是最重要的变化之一。将I/O引脚数量增加两倍,同时保持相似的物理占用空间,对于内存制造商、SoC开发商、代工厂和外包组装和测试 (OSAT) 公司来说极具挑战性。

根据Trendforce去年年底分享的路线图预计,首批HBM4样品预计每堆栈容量高达36GB,完整规格预计将由JEDEC在2024-2025年下半年左右发布,预计第一批客户样品和供货时间是2026年。

今年,DRAM市场的竞争越发白热化。2月,三星电子首次实现了36GB容量的HBM3E 12层高带宽内存(HBM)技术。HBM3E 12层技术通过使用通过硅通孔(TSV)技术堆叠多达12层的DRAM存储芯片,正在成为今年下半年AI半导体市场的关键竞争领域。这一进展加剧了三星电子、SK海力士和美光等内存公司之间的竞争。

据悉,三星已经在第二季度开始大规模生产这款第五代HBM产品,并且正在向特定客户供应。但其仍需要通过质量测试(Qual Test)才能在下半年向NVIDIA供应其HBM3E 12层产品。因此,三星正全力以赴满足NVIDIA的高标准。

SK海力士也在积极准备,计划在第三季度开始大规模生产其HBM3E 12层产品。虽然目前SK海力士向NVIDIA供应的是之前的HBM3E 8层产品。为了加速市场领先地位,SK海力士已经将大规模生产时间表从明年提前到今年的第三季度。

美光作为这场竞争中的黑马,计划在下半年完成HBM3E 12层产品的大规模生产准备工作,并计划在明年向NVIDIA等主要客户供应。

谁能率先向NVIDIA供应HBM3E 12层产品,还有悬念,今年下半年对于决定HBM市场的未来格局至关重要。

奇谱科技

奇谱科技