作者:原创

近日台积电在荷兰阿姆斯特丹举行的开放创新平台(OIP)论坛上宣布,准备在2025年末开始大规模量产N2(2纳米级别)工艺,2026年底开始生产A16(1.6纳米级别)工艺。

台积电设计基础设施管理负责人Dan Kochpatcharin表示:“你们在这里看到的路线图实际上和六个月前在技术研讨会上看到的是同一张,实际上就是同一个技术路线图。我们有N2、N2P,它们将分别在明年和后年投入生产,然后是A16。”

台积电表示,所有这些工艺技术都计划在2026年底为高容量制造(HVM)做好准备。

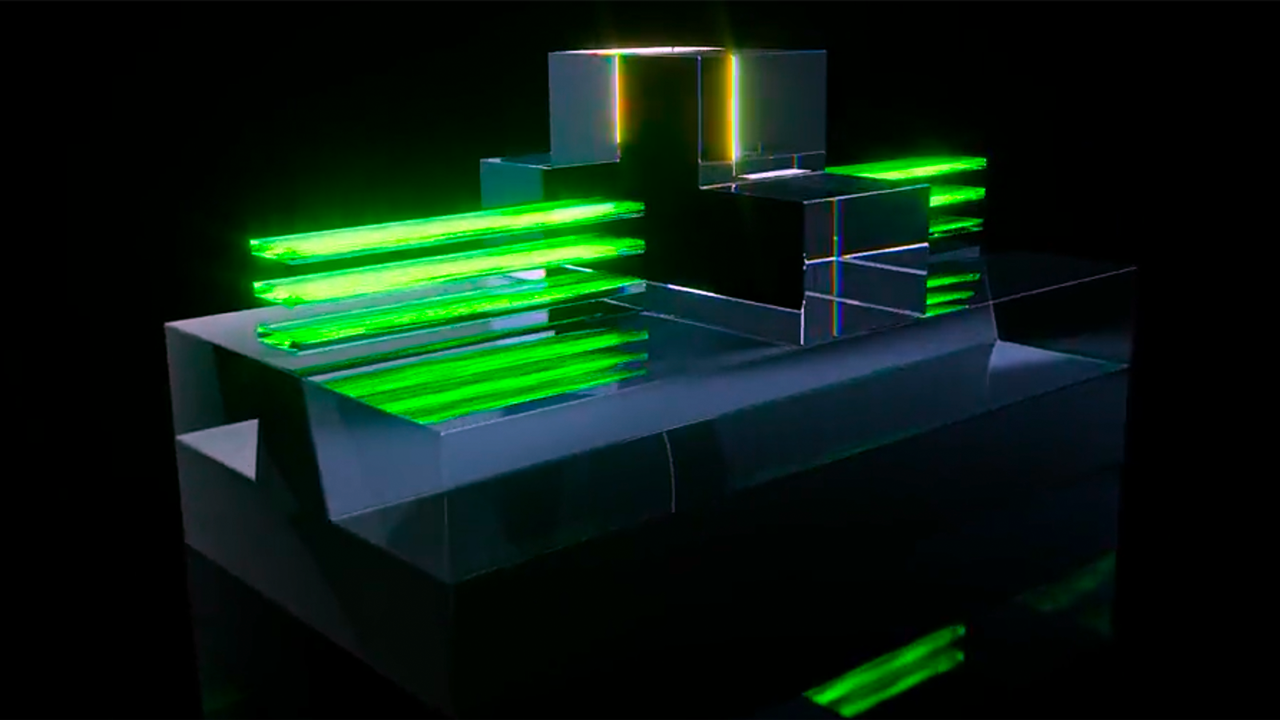

从技术上讲,N2P、N2X和A16有很多相似之处:它们都基于纳米片环绕栅(GAA)晶体管。N2系列使用超高性能金属-绝缘体-金属(SHPMIM)电容器来降低晶体管通孔电阻,以提高性能效率,而A16则使用背面供电网络(BSPDN)来进一步改善性能。

相比于N2P工艺,A16承诺在相同的电压和复杂性下性能提高 8%-10%,或者在相同的频率和晶体管数量下降低15%-20%的功率。此外,台积电估计高端AI处理器的芯片密度将增加1.07倍至1.10倍,具体取决于所使用的晶体管类型和库。

Dan Kochpatcharin说:“A16基本上是带有超级电源轨的N2P,这是我们创新的背面供电网络。” 背部供电技术实现更高的性能和更好的电源效率,但是台积电也指出,这种做法增加了散热的问题,必须要解决。当前实现的BSPDN最适合数据中心级别的AI处理器,这是台积电目前用A16瞄准的市场细分。

至于N2P,它在不增加背面供电相关的复杂性的情况下提高了性能,这对于客户端设备来说是最优的,例如智能手机和入门级PC的系统级芯片(SoC)。当然,N2X通过增加更高的电压进一步提升性能,这可能对各种应用有益,如高性能CPU。

台积电表示,电子设计自动化(EDA)工具和第三方IP模块已经为N2P和N2X工艺技术(2纳米级别)准备就绪,这使得各种芯片设计者能够基于台积电的第二代2纳米级别生产节点开发芯片,从而利用纳米片晶体管和低电阻电容器。

奇谱科技

奇谱科技