作者:原创

在本月初,台积电已完成2nm制程晶圆的试生产工作,良品率高达60%。近日,在IEEE国际电子器件会议(IEDM)上,台积电透露了其N2(2nm)制造工艺的更多细节。

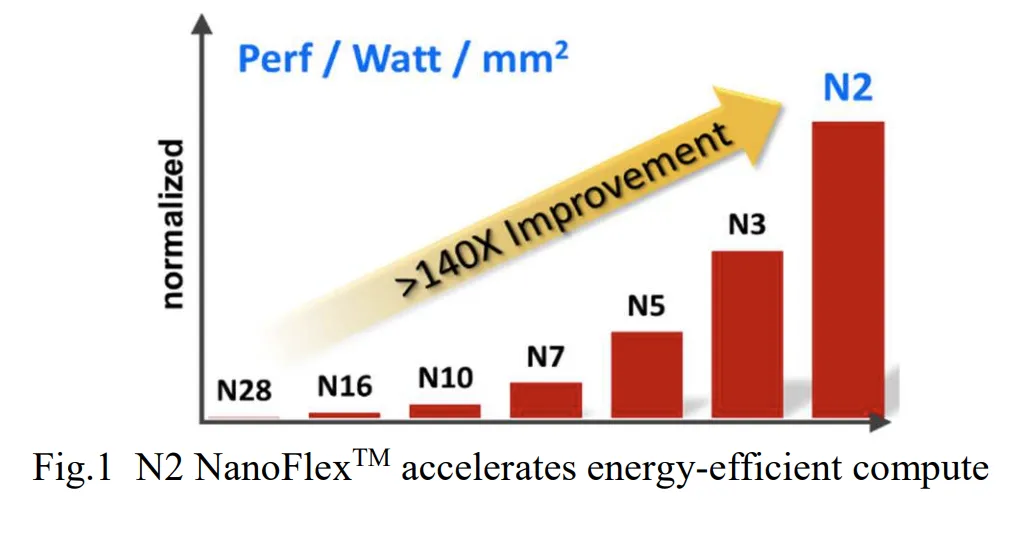

据介绍,N2在相同电压下功耗降低24%-35%,性能提升15%,并且与目前的N3(3nm)工艺相比,晶体管密度提高了1.15倍。这些优势绝大多数是由台积电的新环绕栅极(GAA)纳米片晶体管以及N2 NanoFlex设计技术共同优化能力和其他增强功能实现的。

环绕栅极纳米片晶体管允许设计者调整他们的通道宽度,以平衡性能和功耗效率。此外,台积电的N2增加了NanoFlex DTCO,允许使用不同的纳米片构建不同的逻辑单元,同一芯片上可以有100到2000个纳米片。由窄器件制成的逻辑单元可能构成芯片上的通用逻辑,而那些具有更宽纳米片的逻辑单元(能够驱动更多电流并更快地切换)将构成CPU核心。

N2在工艺和器件层面的创新不仅旨在通过改进薄片厚度、结点、掺杂激活和应力工程来提升晶体管驱动电流,还在降低有效电容(Ceff)以实现领先的能效。总的来说,这些改进使得N型和P型纳米片晶体管的I/CV速度分别提升了约70%和110%。

与FinFET相比,N2纳米片晶体管在0.5V至0.6V的低供电电压范围内,每瓦性能明显更好,工艺和器件优化将时钟速度提高了约20%,并将待机功耗在0.5V操作下减少了约75%。此外,集成N2 NanoFlex和多重阈值电压(multi-Vt)选项为高逻辑密度下的能量高效处理器提供了额外的设计灵活性。

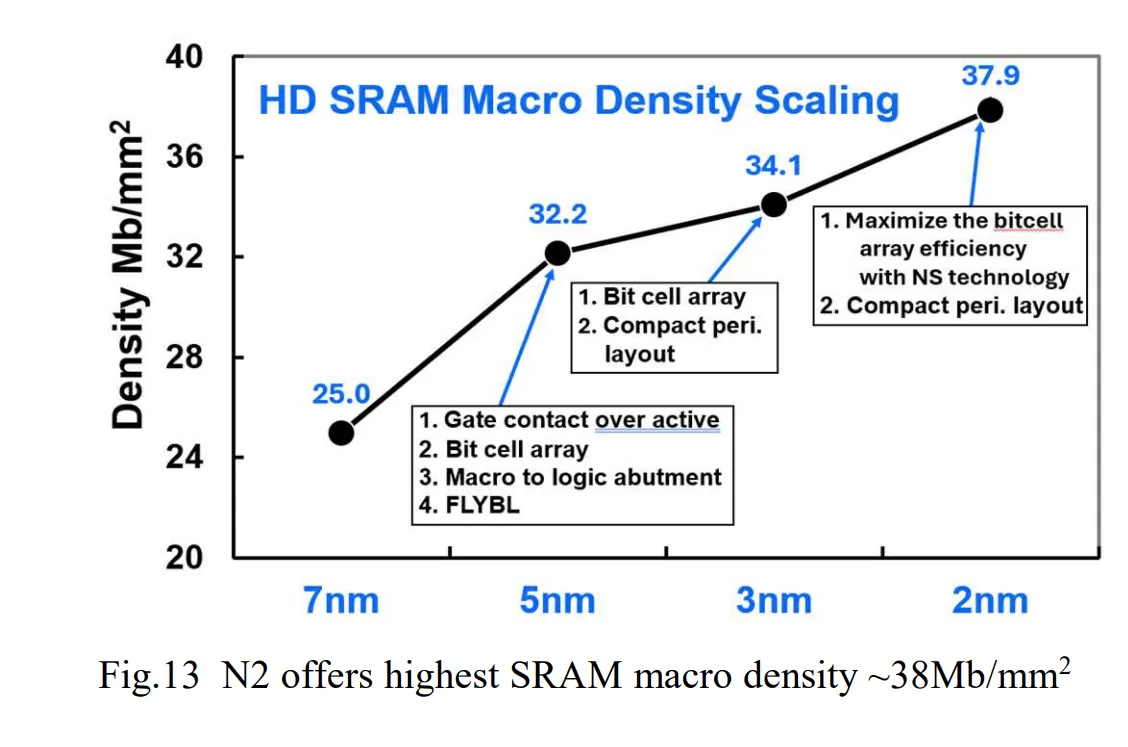

晶体管架构和DTCO优势直接影响SRAM的可扩展性,这在近年来的领先节点中难以实现。有了N2,台积电成功实现了创纪录的2纳米SRAM密度,约为38Mb/mm²。除了达到创纪录的SRAM密度外,还降低了功耗。由于GAA纳米片晶体管具有更紧密的阈值电压变化(Vt-sigma),N2在高电流(HC)宏单元的最小工作电压(Vmin)上比基于FinFET的设计降低了约20毫伏,在高密度(HD)宏单元上降低了30-35毫伏。这些改进使得SRAM在读/写功能稳定在大约0.4V的同时,保持了高产量和可靠性。

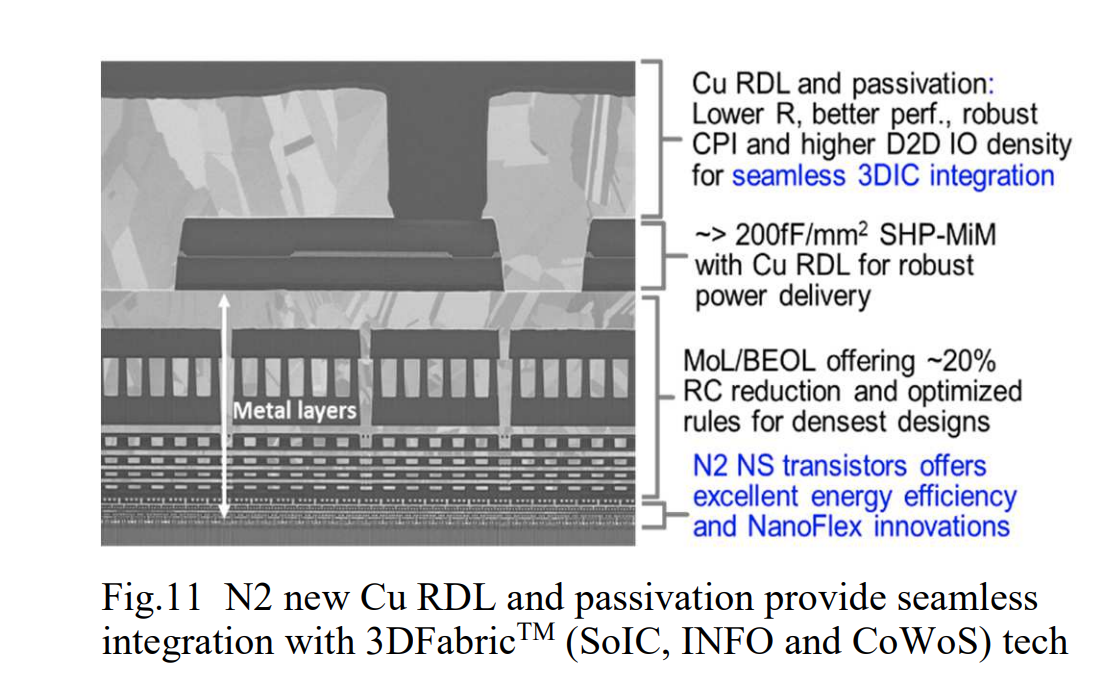

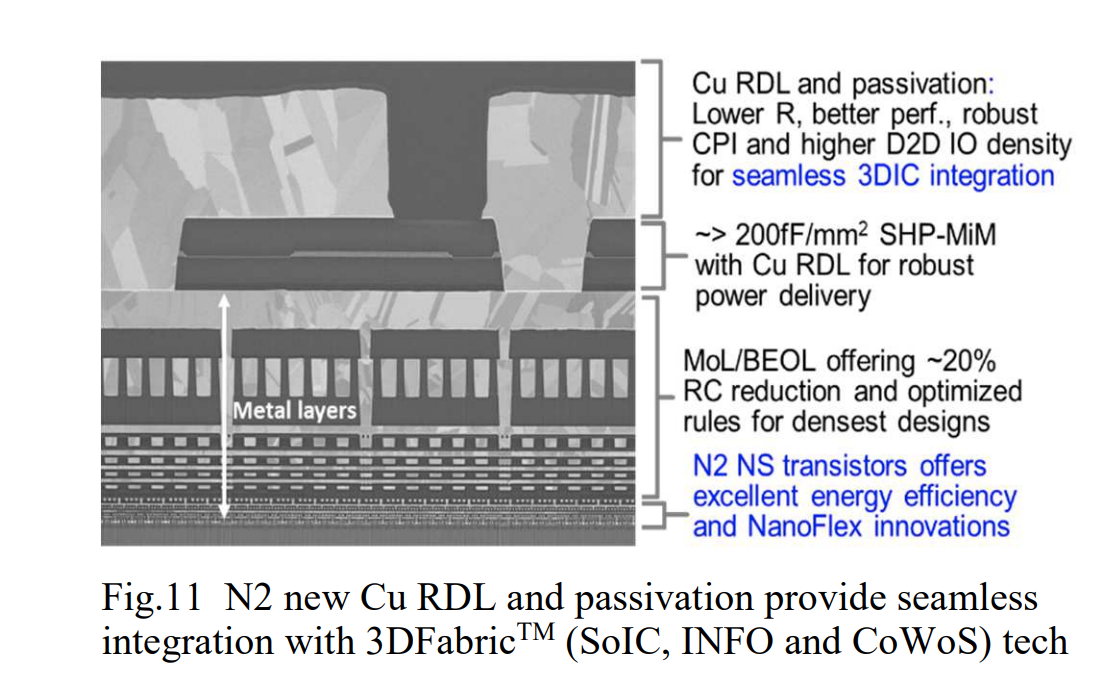

除了新的晶体管,台积电的N2采用了全新的中间线路(MoL)、后端线路(BEOL)和远后端线路(far-BEOL)布线,以减少20%的电阻并提高性能效率。此外,N2为高性能计算(HPC)应用提供的额外特性包括超高性能MiM(SHP-MiM)电容器,提供约200fF/mm²的电容,这有助于通过减少瞬态电压下降来实现更高的最大工作频率(Fmax)。

台积电计划在2025年下半年开始量产N2工艺技术,继续保持业界领先地位。据IDC表示,受人工智能 (AI) 应用和加密挖掘中使用的先进技术的强劲需求推动,台积电预计明年收入将增长约25%,创下新高。

奇谱科技

奇谱科技