作者:原创

国际半导体行业标准组织JEDEC正式发布了HBM4规范JESD270-4,这是一种新的内存标准,旨在跟上人工智能工作负载、高性能计算和先进数据中心环境日益增长的需求。新标准引入了架构变化和接口升级,旨在提高内存带宽、容量和效率,以应对数据密集型应用的持续发展。

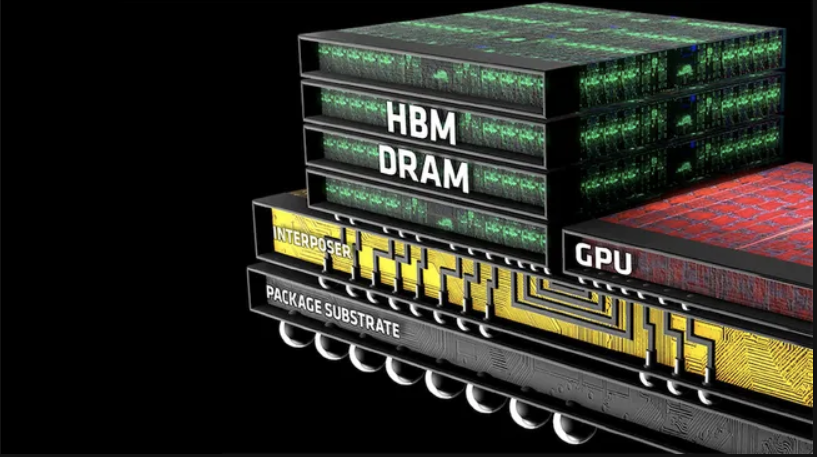

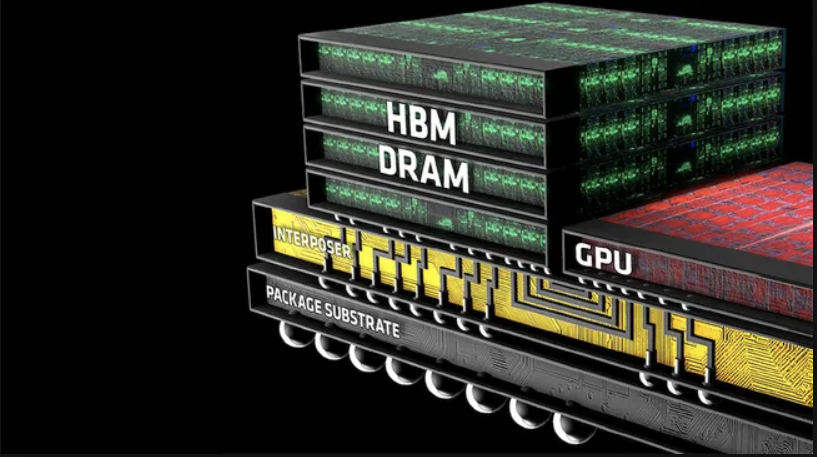

HBM4继续使用垂直堆叠的DRAM芯片,这是HBM系列的标志性特征,但与前代HBM3相比,在带宽、效率和设计灵活性方面都有显著提升。它支持通过2048位接口传输速度高达8Gb/s,总带宽可达2TB/s。其中一项关键升级是每个堆叠的独立通道数量翻倍,从HBM3的16个增加到HBM4的32个,每个通道还包含两个伪通道。这种扩展允许在内存操作中实现更大的访问灵活性和并行性。

在功耗效率方面,JESD270-4规范引入了对一系列供应商特定电压水平的支持,包括 0.7V、0.75V、0.8V或0.9V的VDDQ选项,以及1.0V或1.05V的VDDC选项。这些调整有助于降低功耗,并根据不同的系统需求提高能效。HBM4还保持了与现有HBM3控制器的兼容性,允许单个控制器可以与任一内存标准配合使用。这种向后兼容性简化了采用过程,并允许更灵活的系统设计。

此外,HBM4还引入了定向刷新管理(DRFM),增强了

HBM4的一个显著架构变化是命令总线和数据总线的分离,旨在增强并发性并降低延迟。这一改进旨在提升多通道操作的性能,而多通道操作在人工智能和高性能计算工作负载中非常普遍。此外,HBM4还引入了新的物理接口和信号完整性改进,以支持更高的数据速率和更高的通道效率。

HBM4的开发涉及了三星、美光和SK海力士等主要行业参与者之间的合作,这些公司参与了标准的制定,预计将在不久的将来开始展示兼容HBM4的产品。三星表示计划在2025年开始生产,以满足人工智能芯片制造商和超大规模数据中心日益增长的需求。

奇谱科技

奇谱科技